CoreGEV-Tx10 GigE Vision FPGA IP Core

Transmit uncompressed images over GigE Vision at up to 10 Gbps

Pleora’s CoreGEV-Tx10 GigE Vision FPGA IP Core with Flexible Hybrid Accelerator Architecture helps manufacturers shorten time-to-market, reduce risk, and lower costs by providing robust, low latency and high performance GigE Vision® transmit capability for their sensor system.

The FGPA IP Core supports up to 10 Gbps transmission of uncompressed images over a standard Ethernet connection. CoreGEV-Tx10 is compliant with the GigE Vision and GenICam™ standards, enabling seamless interoperability in multi-vendor networked or point-to-point digital video systems. A flexible, dynamically generated, fully customizable GenICam XML file approach allows users to quickly and easily add custom features.

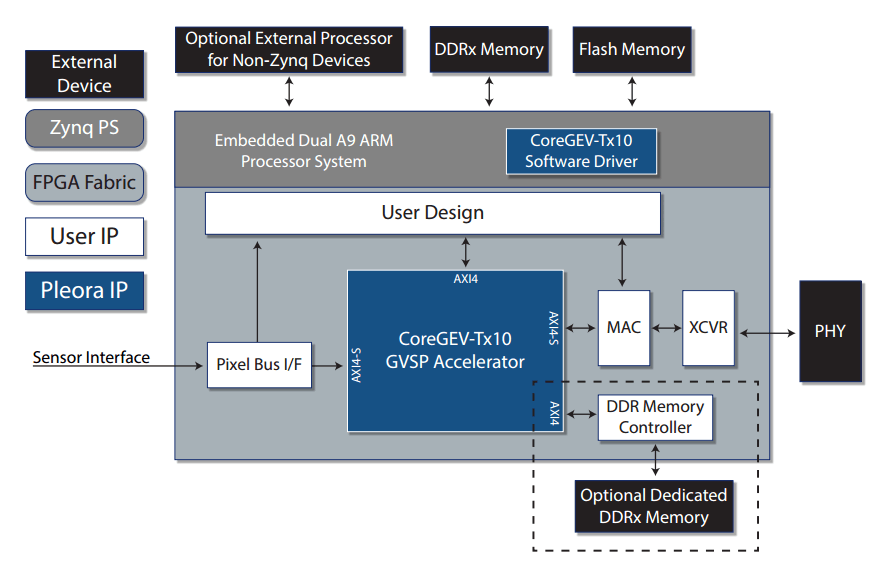

Hybrid FPGA Accelerator Architecture

Pleora’s unique hybrid FPGA accelerator implementation allows users to bring the sensor up using the onboard processor only and a pure software approach for rapid prototyping. Once the FPGA implementation is complete, users switch the software driver to “FPGA Acceleration” mode, using the FPGA to offload the video streaming and enabling up to 10 Gbps of low latency transmission of uncompressed images. The software only method can also be used on slower sensors within a family of sensors, reducing development costs and ensuring a consistent interface for software applications across an entire sensor family or families.

Complete End-to-End Solution

Image streams transmitted by CoreGEV-Tx10 FPGA IP need to be received by the final application, often running on a host PC. Pleora’s eBUS™ Software Development Kit (SDK) is a feature-rich application development toolkit providing comprehensive APIs for controlling GigE Vision sensors and for efficiently receive image streams for processing by the host CPU or GPU. By using eBUS, manufacturers can further shorten time to market and development costs for interfacing their end applications to their sensor.

Key Features

- Supports up to 10 Gbps transmission rates for uncompressed images over standard Ethernet

- Generic AXI ports enable rapid connection to CPU system, memory system, MAC/PHY and video interface

- Low resource utilization for low cost device selection

- GigE Vision 2.0 compliance ensures interoperability in multivendor digital video systems

- GenICam compliant interface provides easy access to programming features and simplifies integration of imaging devices into existing or new systems

- Image management tags an image or group of images with metadata – provides context necessary to retrieve image data from the on-board frame buffer in event of power or network failure at the receiver

- Pleora’s Flexible Hybrid Architecture

- Run full GigE Vision protocol from software-only mode

- Activate CoreGEV driver to allow operation through FPGA for 100% hardware acceleration of GigE Vision for full 10 Gbps throughput

- Get started quicker on designs and implement software from day one in parallel with hardware bring-up

- Firmware allows customer to implement image processing algorithms on a CPU and GPU before transferring to FPGA

- Support for custom GenICam nodes

- Optional dedicated memory interface for highest possible performance

Resources

CoreGEV-Tx10 GigE Vision FPGA IP Core Data Sheet

Download Datasheet

Sensor Networking for Medical and Industrial FPDs

Download BrochureFor additional technical resources log into the Pleora Support Center

Buy Now

CoreGEV-Tx10 Hardware Development Kit

Includes Xilinx Zynq-7000 SoC ZC706 Evaluation Kit, reference design, Aquantia AQS-107 10G SFP+ 10G BASE-T Module, Intel X550-T1 10G PCIe NIC (first kit included with IP Core purchase, additional kits can be purchased)

Contact UsCoreGEV-Tx10 FPGA IP Core

FGPA IP Core supports up to 10 Gbps transmission of uncompressed imaged over a standard Ethernet connection

Contact Us